Zoals sommigen misschien weten ben ik bezig met Chameleon, een ambilight achtig project. Hiervoor moeten natuurlijk de nodige LEDs aangestuurd worden en daarom heeft het printje een set van 12 N-channel MOSFETs die GND schakelen naar de aangesloten LEDs.

Nu bleek dat bij dit prototype nogal wat FETs de geest gaven en ben ik gaan onderzoeken wat het probleem was. Ik denk dat ik ondertussen ook een mogelijke oplossing heb gevonden maar het is misschien handig jullie er ook over te laten mee denken. En misschien interessant voor anderen ook.

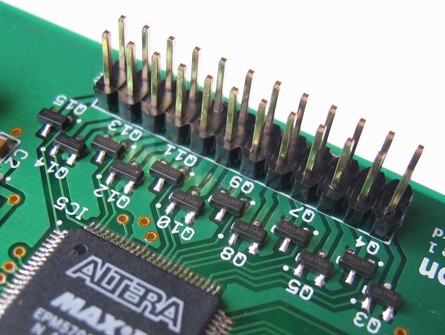

De gebruikte FETs zijn logic level FETs van IRF, in SOT-23 omdat er dan mooi 12 in een kleine ruimte passen:

Wat gegevens en een link naar de datasheet:

IRLML2502

Vdss = 20V, Rdson = 45mΩ

ID max = 4,2A (Vgs=4,5V), Vgs(th) = 1,2V max

Ciss = 740pF, Coss = 90pF

De gates zitten direct op een CPLD met korte verbindingen zoals je ziet. De source en drain zitten beiden aan de pinheader (12 source, 12 drain). De sources zitten bovendien allemaal aan het grondvlak vast.

Een aantal FETs bleek op een gegeven moment doorgebrand. Hoewel ze nog wel werkten gingen ze niet helemaal goed meer dicht maar lieten een tiende van de aan-stroom nog door in uit-stand. Hierdoor werden ze flink warm omdat door de kleine stroom een groot deel van de spanning over de FET ipv de load staat. Zelfs bij 200mA stroom werden ze al heet genoeg om onprettig te voelen aan je vinger, en bij een FET die continu uit stond liep toch nog zo'n 50mA en werd de FET ook merkbaar warm.

Omdat ze nog wel redelijk werkten viel het niet direct op dat ze stuk waren, later met een nieuwe FET getest en deze bleek correct te werken met een 10Ω load tot een spanning van 10V. Ook al liep er ongeveer 1A de FET werd niet warm. Maar bij 12V op de load sloeg deze ineens door en werd gloeiend heet. Daarna vertoonde de FET hetzelfde gedrag als de andere kapotte.

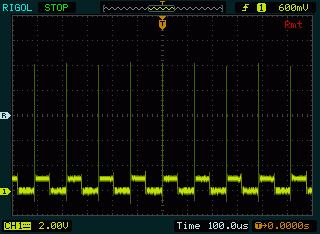

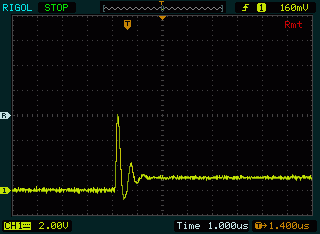

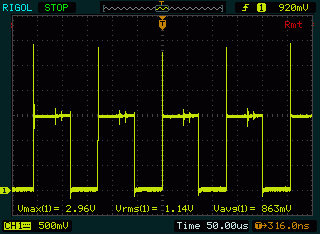

M'n vermoeden dat de max 20V van de FET misschien was overschreden door een piek leek te kloppen gezien de scope beelden. Dit is de drain met een 10Ω load op 1V (!), afkomstig van een labvoeding.

Hoewel de load gewoon een weerstand was en dus niet erg inductief zou moeten zijn kwamen er toch flinke spikes op de drain. Hier zo'n 8V spike met een load op 1V (0,1A). Bij hogere spanningen wordt de spike ook flink hoger.

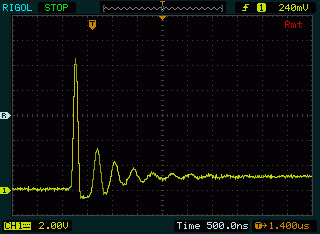

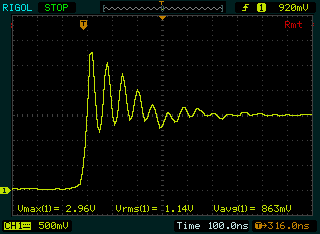

Detail van de spike (en wat ringing):

Voor de volledigheid de gate aansturing nog even (3,3V logica):

Dit is overigens met de outputs op 4mA current limit om te kijken of dat zou schelen (minder snel schakelen), zonder current limit is de rise en fall time ongeveer 100ns. Wat snel genoeg zou moeten zijn, de PWM frequentie is 7kHz.

Een diode over de load heeft weinig zin met een ohmse load en haalde ook niets uit. Het enige dat nog inductief is zijn de aansluitdraden naar de labvoeding en tussen het printje en load. Het waren geen meters maar toch relatief lange kabels.

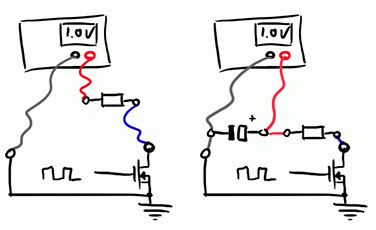

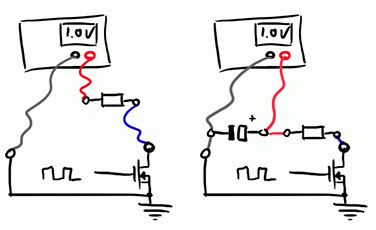

De load dichter bij het printje zetten werkte ook niet, maar een condensator over de + en - van de labvoeding, dicht bij de load en het printje (rechts op het plaatje) deed wonderen, de piek was vrijwel verdwenen.

Probleem is dat er normaal gesproken wel lange kabels aan zitten, het gaat immers om verlichting en dat zit meestal wel een eindje af van de voeding en het printje. Bovendien moet het bordje ook door anderen gebruikt en aangesloten gaan worden dus wel wat fool proof zijn en niet stuk gaan als je niet toevallig een condensator op een bepaalde plek zet. Het wordt dus uiteindelijk toch zoals op het linker plaatje.

Andere oplossing zou misschien een snubber zijn op de drain. Een 50Ω weerstand in serie met 470pF (op de load, niet helemaal op de print gezien het lastig is dat aan te passen) scheelde wel bijna de helft maar nog steeds een flinke piek:

Ook 470pF zonder weerstand of direct 470pF over de pootjes van de FET gaf ongeveer hetzelfde effect.

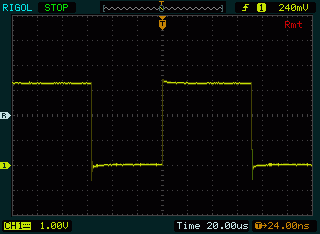

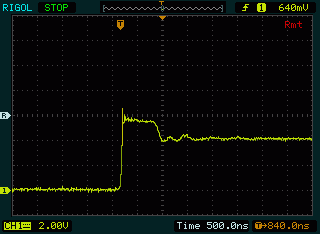

Een betere oplossing bleek een zener diode. De grootste die ik had was 5,1V. Deze direct over source en drain van de FET gehouden en de spike was weg, of beter gezegd beperkt tot net onder 6V:

Nu met 4V op de load (wat eerst niet mogelijk was door de enorme piek die het zou veroorzaken) en de piek blijft mooi net boven 5,1V hangen om vervolgens netjes te zakken op 4V load.

Is dit een beetje een nette oplossing voor het probleem? Ik dacht dat zeners hiervoor te traag zouden zijn, misschien nog een kleine condensator parallel zetten voor de ergste piek? Het scoopbeeld ziet het er goed uit, maar de probe voegt natuurlijk ook weer wat capaciteit toe dus misschien zit er nog steeds een snelle piek?

Een ander probleem is (was?) dat er storing via de composiet ingang op het bordje naar de video bron gekoppeld wordt. Er is in beeld een streep te zien die langzaam langs het beeld loopt als het bordje is aangesloten. Als de composiet ingang losgekoppeld wordt verdwijnt de streep, het lijkt dus geen storing door de lucht. Misschien dat dit probleem wel door de pieken veroorzaakt werd, ik heb het nog niet getest met zeners erop omdat ik die niet voor 12V heb en het wat lastig aan te sluiten is allemaal. Sinds de FETs stuk begonnen te gaan heb ik geen zware load meer op de FETs gezet.

Het kan ook zijn dat de storing door het schakelen van de gates gaat, het is toch 740pF per gate. Misschien is het handig nog ene kleine serieweerstand te plaatsen tussen CPLD (wordt FPGA later) en de gate van de FET. Maar scoopbeelden van de gate geven een mooie snelle golf zonder veel ringing dus of het echt nodig is weet ik niet. Het kan ook de voeding zijn (1.8V analoog en digitaal) waar de storing doorheen komt. Maar goed, zal eerst wel kijken of het spike probleem dit veroorzaakte, anders valt er ook weinig over te zeggen.

De LEDs worden waarschijnlijk wel met kabels aangesloten die gauw een meter zijn, zou dit nog voor veel storing door de lucht zorgen in combinatie met PWM? De frequentie is nu 7kHz maar het is misschien handiger deze boven de 20kHz te zetten zodat je mogelijke storing niet zo gauw hoort. Per kanaal zal de stroom maximaal zo'n 500mA zijn (waarschijnlijk minder), maximaal dus 12 kanalen. Strips en bekabeling komt waarschijnlijk wel dicht op de TV dus het zou vervelend zijn als je hier allemaal interferentie door krijgt. Ik heb met EMI weinig ervaring en het is ook een lastig iets volgens mij. Misschien geeft langzamer schakelen van de FETs ook minder interferentie, wel meer schakelverliezen maar met relatief lage frequenties moet dat niet zo'n probleem zijn. Wel kunnen de SOT-23 packages natuurlijk maar weinig verlies hebben voordat ze gloeiend heet worden. Als iemand nog goede tips heeft voor het schakelen van de FETs zodat je het minste last hebt van EMI zijn die zeker welkom.

Een aantal ideeen kan ik je wel geven:

Die fets zullen bij zeer snel schakelen (wat ze doen in jou geval) wel een aardig stroompje trekken, in de orde van enkele 10-tallen mA als je een 1A load aanstuurt. Met de snelheid van die CPLD (rise/fall-times) gaat dit zowiezo voor redelijke spikes op de digitale voeding zorgen. Als de analoge/digitale van dezelfde hoofdbron komen, heb je daar het antwoord voor de storing op je composiet.

ongeveer 68ohm - 100ohm gate serieweerstanden gaat er al voor zorgen dat schakelspikes op de voeding een heel stuk minder worden. Ook moet die CPLD op elke voedingspin ontkoppeld zijn. Als 'ie drie voedingspinnen heeft, 3 100nF, allen gebufferd door een gemeenschappelijke 10u - 47u elcotje.

Waar de spike vandaan komt bij het schakelen heb ik geen idee van. Zoals je al aangaf, waarschijnlijk de inductie van de voedingskabels door de load/drain.

Een andere mogelijkheid is dat de interne inducties in de fets parten gaan spelen bij het snelle schakelen zonder gate weerstand. Kijk maar eens in de datasheet of / hoeveel uH de drain/source inducties zijn.

Omdat je uiteindelijke PWM toch enorm traag is ten opzichte van de schakelflanken, kun je het schakelen prima kunstmatig vertragen met voorgenoemde gate weerstand. Sla je twee vliegen in 1 klap: Altera zal minder spiken op z'n voeding doordat 'ie minder stroom hoeft te sourcen/sinken naar de gates. En verder nog doordat je de flanken minder steil maakt, de invloed van minimale inducties sterk vermindert.

EDIT: Ik had dezelfde problemen met een LED PWM schakeling via een ATmega. Die hebben n.l. ook een zeer rappe rise/fall-time op hun poortpinnen. Ik heb elke load van een PNP stuurtrap voorzien. Dit zorde er voor dat de ATmega niet meer hoefde te sourcen vanaf zijn Vcc, dus spikes waren vrijwel niet meer aanwezig. De te sinken stroom was minimaal door de hoge HFE van BC558C'tjes. Dan zorgen dat je de voeding die naar de emitters gaat met een dikke elco en 220nF C afbufferen wat er voor zorgt dat de voeding die de PWM load voedt goed ontkoppeld wordt van de rest van het systeem.

[Bericht gewijzigd door MagicBox op (16%)]

Ik kan me volledig aansluiten wat MagicBox reeds gemeld heeft. Trouwens ik dacht over die serie weerstandjes daar vroeger bij je ontwerp ook die aanbeveling gedaan te hebben. Naast de reeds opgesomde voordelen heeft een serieweerstandje ook nog een bijkomende beveiliging als er iets foutief met je output gebeurd. Het zou anders best kunnen dat de CPLD/FPGa eens de geest geeft vanwege een te hoge spanning en/of stroom terugvoer bij problemen.

Je gebruikte FET's met een Vdss = 20V vindt ik persoonlijk te laag. Er is weinig marge voor spikes, en spikes zijn echt dodelijk. Trouwens je meting geef ook niet de max amplitude wegens zijn beperkte bandbreedte. Ze zullen nog een stuk hoger zijn.

Ik zou liever een Vdss zien van 50V of hoger. In veel van mijn toepassingen zit tussen logic en eintrap nog een extra diode om bij doorslag niet tot aan je CPLD/FPGA te gaan. Vergeet ook niet dat een kleine soldeerfout fataal kan zijn bij directe aansluiting.

Door de melding van deze problemen verhoogt dit nog meer mijn aandacht gezien ik ook bezig ben met mijn moodlight systeem waar 384 pwm stuurpunten aanliggen.

Neem van mij gerust aan dat printjes maken voor andere gebruikers met I/O's die zonder enige vorm van beveiliging naar buiten gaan, er een heel boel gebruikers zullen zijn die in het startfaze de boel opblazen.

Over EMI, daar zou je best ook nog wat testen uitvoeren. Bij deze stromen en aantallen waarbij vrij veel bekabeling aanwezig is valt hier wel een en ander te verwachten. Moest je een keuring moeten passeren dan denk ik niet dat je zou slagen. Vandaar dat een afstelling van de stuurflanken tov warmte ontwikkeling in de fets ook belangrijk zou kunnen zijn.

Bedankt voor jullie ideeën.

Op 29 september 2007 17:25:28 schreef MagicBox:

Die fets zullen bij zeer snel schakelen (wat ze doen in jou geval) wel een aardig stroompje trekken, in de orde van enkele 10-tallen mA als je een 1A load aanstuurt. Met de snelheid van die CPLD (rise/fall-times) gaat dit zowiezo voor redelijke spikes op de digitale voeding zorgen. Als de analoge/digitale van dezelfde hoofdbron komen, heb je daar het antwoord voor de storing op je composiet.

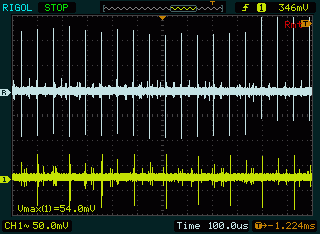

Je hebt gelijk denk ik, de CPLD heeft een core spanning van 1.8V en deelt deze met de analoge 1.8V van de video decoder. Er zit wel een LC filtertje op beide lijnen maar dezelfde regelaar. De I/O van de CPLD zit op 3.3V dus daar zou de grootste stroom vandaan moeten komen lijkt me maar een meting laat zien dat er flink wat van de pieken op de 1.8V terecht komt:

Dit is met 1 PWM kanaal op 1,3V en 50mA gemiddeld, bovenste is zonder zener op de FET, onderste met. Als ik m'n audio boxen in de buurt zet - deze zijn heel gevoelig voor storing, ik ontvang er soms zelfs radio op - hoor ik zonder zener de boxen piepen. Met zener verdwijnt het gepiep.

Bij zwaardere load zal het alleen maar erger worden. In het volgende ontwerp komt sowieso de 1,8V lijn vrij van digitale signalen, omdat de CPLD een FPGA wordt en deze op 1,2V werkt. 1,8V heeft dan een eigen regelaar en is alleen voor analoog. Waarschijnlijk scheelt dat al flink.

ongeveer 68ohm - 100ohm gate serieweerstanden gaat er al voor zorgen dat schakelspikes op de voeding een heel stuk minder worden.

Goed plan, kan makkelijk met een weerstand array.

Ook moet die CPLD op elke voedingspin ontkoppeld zijn. Als 'ie drie voedingspinnen heeft, 3 100nF, allen gebufferd door een gemeenschappelijke 10u - 47u elcotje.

Dat heeft ie wel, ze zitten op de onderkant van de print maar elk voedingspaar heeft een X7R 100nF.

[...]Een andere mogelijkheid is dat de interne inducties in de fets parten gaan spelen bij het snelle schakelen zonder gate weerstand. Kijk maar eens in de datasheet of / hoeveel uH de drain/source inducties zijn.

Zal het eens opzoeken.

EDIT: Ik had dezelfde problemen met een LED PWM schakeling via een ATmega. Die hebben n.l. ook een zeer rappe rise/fall-time op hun poortpinnen. Ik heb elke load van een PNP stuurtrap voorzien. Dit zorde er voor dat de ATmega niet meer hoefde te sourcen vanaf zijn Vcc, dus spikes waren vrijwel niet meer aanwezig. De te sinken stroom was minimaal door de hoge HFE van BC558C'tjes. Dan zorgen dat je de voeding die naar de emitters gaat met een dikke elco en 220nF C afbufferen wat er voor zorgt dat de voeding die de PWM load voedt goed ontkoppeld wordt van de rest van het systeem.

Ik heb ook nog aan losse FET drivers gedacht maar voor 12 stuks en zonder te veel ruimte in te nemen valt dat nog niet mee. Ook de kosten zijn een belangrijk punt en ik denk dat drivers een beetje overkill zijn. De CPLD lijkt geen moeite te hebben met de gate capaciteit, voor power FETs is die overigens nog relatief klein.

Op 29 september 2007 18:43:56 schreef fotoopa:

Ik kan me volledig aansluiten wat MagicBox reeds gemeld heeft. Trouwens ik dacht over die serie weerstandjes daar vroeger bij je ontwerp ook die aanbeveling gedaan te hebben. Naast de reeds opgesomde voordelen heeft een serieweerstandje ook nog een bijkomende beveiliging als er iets foutief met je output gebeurd. Het zou anders best kunnen dat de CPLD/FPGa eens de geest geeft vanwege een te hoge spanning en/of stroom terugvoer bij problemen.

De serieweerstanden komen er zeker in in het volgende prototype.

Je gebruikte FET's met een Vdss = 20V vindt ik persoonlijk te laag. Er is weinig marge voor spikes, en spikes zijn echt dodelijk.

Helaas zijn de goede eigenschappen van FETs meestal omgekeerd evenredig met de Vdss. Het is wel fijn een lage RDSon, kleine SOT-23 package en een lage gate capaciteit te kunnen houden. Bovendien zijn de spikes flink hoog, een hogere Vdss klinkt meer als symptoombestrijding dan een echte oplossing.

Trouwens je meting geef ook niet de max amplitude wegens zijn beperkte bandbreedte. Ze zullen nog een stuk hoger zijn.

Daar ben ik bang voor, ik vraag me daarom ook af of de zener genoeg is, of dat deze stiekem nog een snelle schakelpuls doorlaat zonder dat de scope dit kan opmerken.

[...]Door de melding van deze problemen verhoogt dit nog meer mijn aandacht gezien ik ook bezig ben met mijn moodlight systeem waar 384 pwm stuurpunten aanliggen.

Zeker, ik had ook al in dat topic gekeken of daar al over nagedacht was.

Neem van mij gerust aan dat printjes maken voor andere gebruikers met I/O's die zonder enige vorm van beveiliging naar buiten gaan, er een heel boel gebruikers zullen zijn die in het startfaze de boel opblazen.

In principe wordt de enige interface de source en drain van de FETs. Dit valt wel enigszins te beveiligen maar het is lastig er echt veel aan te doen. Het zijn uitgangen voor hoge stromen, geen digitale I/O waar je wat schottky's op zet naar de voedingslijnen. Als je direct 12V op de drain zet (wat ik tijdens het testen wel eens per ongeluk gedaan heb) is het binnen een fractie van een seconde over met de FET. SOT-23 is niet erg vergevingsgezind wat betreft dissipatie. Overigens is de CPLD na al dit geweld nog steeds heel gebleven. Serieweerstanden in de gate scheelt al in de problemen, maar tegen te hoge drain stroom kun je denk ik weinig doen. Gelukkig gaat in zo'n geval meestal alleen de FET stuk. Als iemand nog goede ideeën heeft voor de beveiliging hoor ik dat graag.

Maar zoiets als die spikes daar moet het bordje gewoon mee om kunnen gaan natuurlijk, omdat zoiets blijkbaar al voorkomt als je de boel op een normale manier aansluit.

Het is ook niet echt de bedoeling dat mensen zelf het bordje gaan solderen, hoewel er natuurlijk mensen zijn die dat gewoon kunnen (heb het zelf tenslotte ook gedaan) is dat een grote mogelijke bron van problemen, zeker als mensen zichzelf iets overschatten.

Over EMI, daar zou je best ook nog wat testen uitvoeren. Bij deze stromen en aantallen waarbij vrij veel bekabeling aanwezig is valt hier wel een en ander te verwachten. Moest je een keuring moeten passeren dan denk ik niet dat je zou slagen.

Met dit bordje zeker niet nee  Keuring hoeft op zich niet, de bedoeling is voorlopig dat het een kit wordt voor mensen die toch wel wat elektronica kennis hebben. Maar het moet natuurlijk niet voor storingen in je TV zorgen, dan heb je ook niets aan zoiets.

Keuring hoeft op zich niet, de bedoeling is voorlopig dat het een kit wordt voor mensen die toch wel wat elektronica kennis hebben. Maar het moet natuurlijk niet voor storingen in je TV zorgen, dan heb je ook niets aan zoiets.

Vandaar dat een afstelling van de stuurflanken tov warmte ontwikkeling in de fets ook belangrijk zou kunnen zijn.

Ja ik denk dat wat langzamer schakelen zeker bevorderlijk is voor de EMI problemen. PWMen door lange draden klinkt als een grote bron van EMI, ik weet niet of daar veel aan te doen valt. Misschien kabels afschermen. Lagere frequenties gebruiken scheelt waarschijnlijk ook, maar hoorbare (of hele lage, in de LEDs zichtbare) frequenties zijn ook weer nadelig.

[Bericht gewijzigd door madwizard op (28%)]

Is het niet practischer het ontwerp in meerdere stukken te hakken? In elke led module een eigen PWM controller? En dan via een serieel protocolletje vanaf de centrale controller die module dingen aansturen?

Digitale hoogohmige signalen zullen voor minder EMI en storing zorgen dan die zeer laagohmige PWM signalen. Ik bedoel ohmig, niet frequent. PWM -> laagohmige load op 'medium' frequentie. Digitale communicatie -> hoogohmig op 'high' freqentie.

Voordeel is dat dan alle PWM gerelateerde signaal lijnen erg kort zijn, de totale load beperkt zich dan tot die ene module.

EDIT: Nog wat anders... kun je bij die Altera CPLD niet de slewrate van de uitgangen instellen? Bij Xilinx CPLDs kun je dat.. of 'SLOW' of 'FAST'. Op 'SLOW' zijn de fall/rise times ruim 50nS ipv 5nS.

[Bericht gewijzigd door MagicBox op (15%)]

Ik denk dat dat een goed idee is. Het maakt het ook makkelijker het aantal LED modules uit te breiden of er juist minder te nemen als je er geen 4 wilt. Zal wel ietsje duurder worden maar het lost wel heel veel EMI problemen op.

Eens kijken of er een mooie kant en klare PWM controller bestaat die 3 FETs aan kan sturen. Kleine uController kan natuurlijk ook maar het zou makkelijk zijn als die controllers niet geprogrammeerd hoeven te worden.

Of je de slewrate kan aanpassen weet ik niet, zou kunnen. Wel een current limit in ieder geval, dan veranderd de rise time in enkele honderden ns.

pros

Prosper, yop la boum, c'est le roi du macadam (aldus Maurice Chevalier)

Op 29 september 2007 16:24:09 schreef madwizard:

Is dit een beetje een nette oplossing voor het probleem? Ik dacht dat zeners hiervoor te traag zouden zijn, misschien nog een kleine condensator parallel zetten voor de ergste piek?

Zo tussendoor: zeners hebben van huis uit al een aardige hoeveelheid parasitaire capaciteit aan boord. En soms heeft dat zijn nut...

Op 29 september 2007 19:53:54 schreef MagicBox:

Is het niet practischer het ontwerp in meerdere stukken te hakken? In elke led module een eigen PWM controller? En dan via een serieel protocolletje vanaf de centrale controller die module dingen aansturen?

Bij mij gaat dit ook niet, met in totaal 384 pwm's is dit niet te doen. Maar ik zal vermoedelijk de FET's direct bij de leds plaatsen ( power) en een transistor trapje ertussen. Dient tevens voor beveiliging tuusen FPGA en powerleds. Driverkabels zijn twisted-pair afgeschermde kabels (vb 10 pair) en moeten enkel de bcxxx sturen. Mijn pwm's draaien op 8Khz ( 128 usec volle pulsbreedte via een 2MHz pwm clk en 256 steps)

slewrate in de FPGA in Quartus kun je idd ook instellen.

Je kunt ook net als deze 30 jaar oude driver http://focus.ti.com/lit/ds/symlink/uln2003a.pdf een common lijn maken en die aan de voeding hangen van de aan te sturen schakeling. Al dan niet met een lokaal condensatortje op je bord.

Op 29 september 2007 21:05:35 schreef jojo:

Je kunt ook net als deze 30 jaar oude driver http://focus.ti.com/lit/ds/symlink/uln2003a.pdf een common lijn maken en die aan de voeding hangen van de aan te sturen schakeling. Al dan niet met een lokaal condensatortje op je bord.

Die ULN2xxx is te traag voor een kleinste pulse van 500 nsec (pwm clock is 2MHz).

Dat bedoel ik niet. Hij maakt zijn eigen driver. Maak dan ook iets dergelijks als in de ULN zit er bij door een setje 1n4148's o.i.d. naar een common lijn te leiden.

Het probleem is idd de inductie van aansluitingen, icm. snelle fall times.

jojo's oplossing vind ik mooier dan een stel zeners. Wel de "common" goed lokaal ontkoppelen met een MLCC'tje.

Hoe dan ook zal je ook gate weerstanden nodig hebben. Ik vind 100 ohm nog wat aan de kleine kant voor dergelijk kleine fet's. Als je de capaciteiten van de fet kent (datasheet), kan je de rise/fall time uitrekenen ifv. de gate weerstand.

Op 29 september 2007 20:22:33 schreef pros:

Zo tussendoor: zeners hebben van huis uit al een aardige hoeveelheid parasitaire capaciteit aan boord. En soms heeft dat zijn nut...

Misschien is dat al voldoende ja.

Zoiets als de ULN werkt misschien ook wel, maar als de LED voeding (GND en 12V) niet dicht bij het printje zit zal de ontkoppeling wel erg belangrijk zijn. Ik heb wel wat met een schottky getest maar zonder ontkoppeling van de 12V dicht bij het printje. Dat zal ik nog eens proberen. Ik wilde liever niet de 12V op het printje zetten maar als het wel goed werkt met een diode is dat inderdaad mooier dan met zeners.

Hoe dan ook staat het idee van losse controllers me wel aan, zelfs als alles met de FETs is opgelost houdt je nog steeds een flinke pulsstroom in de kabels. Met een losse controller kan je de kabels met hoge stromen kort houden. Ook haal je de schakelpulsen van het hoofd printje af wat weer bevorderlijk is voor het analoge deel.

Vermogengedeelte afzonderlijkplaatsen is zeker een betere oplossing. Je hebt al een nadeel met je pcb die slechts dubbellaags is. Eigenlijk is dit al heel kritisch voor FPGA's. Er is veel meer dan de baantjes te kunnen routen. Maar voor de hobby is er maar weinig alternatief.

Modulair is het ook beter. Je behoud een vrij universeele unit die iets kan sturen. Wat je stuurt maakt dan niet zoveel uit. Door je powertrap afzonderlijk te maken ben je niet beperkt in type, spanning of stroom. Je stuurdraden blijven beperkt in spannings niveau's en driven minder stroom.

De pwm zou ik op de FPGAmodule laten. Je kunt ze dan gewoon gebruiken, of gemultipexed of in het eerder welke configuratie. Ik heb gekozen voor multiplex in 1:8 maar niets belet ermij te kiezen tussen 1:1 en 1:16

De rise/fall time bij de ULN types zullen zeker gunstiger uitvallen. Maar je bent meer beperkt voor de gebruikte spanningen, stroomen en ze hebben ook een nogal hoge verliesspanning over de CE. Qua prijs vallen ze gunstig uit en ze monteren gemakkelijk in groepen van 8. Meer voor mij blijven ze net iets te traag.

Je huidige pcb moet eigenlijk maar lichtjes gewijzigd worden. Als je in de gates van je fets een weerstandje aanbrengt heb je alle mogelijkheden om de schakelflank te regelen samen met je instellingen in Quartus. Je fet types mogen zelfs blijven, ze zijn perfect bruikbaar voor gewone toepassingen waar geen hoge powers nodig zijn. Monteer dan de echte vermogenfets bij je verbruiker en neem daar iets hogere spanningen, 50V minimaal maar mag ook hoger zijn. Die fets moeten geen logic level hebben. De hoge stromen komen niet op je pcb print en worden ook niet door je draden gestuurd. Je onwerp blijft vrij universeel bruikbaar voor vele andere toepassingen. Je FPGA is beveiligd tegen vreemde externe spanningen.

[Bericht gewijzigd door fotoopa op (24%)]

Nog even over de clamp diodes: Het zal werken, maar valt ook weer onder symptoom bestrijding. Tevens stook je vermogen weg in die diodes als de spikes erg hoog zijn. Je hoeft welliswaar geen zware diodes te nemen, maar het is toch een deel aan vermogen dat je weggooit. Zulk soort diodes moeten dien als bescherming voor foutsituaties, niet als oplossingen.

Met clamp-zenerdiodes, akkoord. Met diodeclamps naar de voeding, nee. Je inductiepiek wordt gewoon terug in de voeding geduwd. Je hebt enkel een beetje verlies in de diode, maar het grootste deel van de energie wordt gerecupereerd.

Een ander voordeel van zo'n diodeclamp is dat die onafhankelijk is van de voedingsspanning. Je kan gelijk welke voeding gebruiken, als de FET het maar slikt.

Op 30 september 2007 08:11:25 schreef fotoopa:

Vermogengedeelte afzonderlijkplaatsen is zeker een betere oplossing. Je hebt al een nadeel met je pcb die slechts dubbellaags is. Eigenlijk is dit al heel kritisch voor FPGA's. Er is veel meer dan de baantjes te kunnen routen. Maar voor de hobby is er maar weinig alternatief.

Ik denk dat het wel meevalt met dubbellaags, er gaan geen gigantisch snelle signalen doorheen en de boel is goed ontkoppeld. De videodecoder zit op 27MHz en werkt perfect, de beeldkwaliteit (hoewel niet zo belangrijk in mijn geval) is boven verwachting.

Vier lagen is mooier, maar vaak het dubbele in prijs voor zowel fabricage als de software waarmee je het printje maakt.

[...]De pwm zou ik op de FPGAmodule laten. Je kunt ze dan gewoon gebruiken, of gemultipexed of in het eerder welke configuratie. Ik heb gekozen voor multiplex in 1:8 maar niets belet ermij te kiezen tussen 1:1 en 1:16

Bij mij is er geen multiplexing, maar PWM op de FPGA betekent wel dat er nog steeds 12 (eigenlijk 16 met GND) draden naar de modules moeten. Want elke module moet onafhankelijk gestuurd worden. Zonder 'intelligente' module moet voor je elk kanaal los een draad maken.

Met een kleine microcontroller op de module heb je nog maar 2 draden nodig (3 met voeding), die je ook kunt doorlussen naar de andere modules. Nadeel is weer dat je die weer los moet programmeren (het printje zelf kan nu volledig via USB geprogrammeerd worden, zonder andere hardware). En dat ze een voeding nodig hebben voor zichzelf (regelaar op de module (meer kosten) of voedingsdraad maken (meer draden)).

Je huidige pcb moet eigenlijk maar lichtjes gewijzigd worden. Als je in de gates van je fets een weerstandje aanbrengt heb je alle mogelijkheden om de schakelflank te regelen samen met je instellingen in Quartus. Je fet types mogen zelfs blijven, ze zijn perfect bruikbaar voor gewone toepassingen waar geen hoge powers nodig zijn.

Je bedoelt die FETs als sturing te gebruiken voor de andere FETs? Wel een beetje zonde van die FETs. Het zijn wel degelijk power FETs, ook al zijn ze klein. Het is niet een 2N7002 (BS170).

Monteer dan de echte vermogenfets bij je verbruiker en neem daar iets hogere spanningen, 50V minimaal maar mag ook hoger zijn. Die fets moeten geen logic level hebben.

Waarom niet? Zoals ik zei zijn de huidige FETs gewoon power FETs. Niet in de orde van 50A maar dat is ook overkill. Ze kunnen 4,3A hebben als je ze goed open stuurt (4,5V) maar mijn doel is ongeveer 1A en dat gaat prima met 3,3V aanstuur logica. Afgezien van de pieken werkt een 1A stroom bijvoorbeeld prima, de FET wordt niet voelbaar warm. Veel hogere stromen zullen niet nodig zijn. Elk kanaal is 1 kleur, dus je hebt al 3A totaal per strip wat je kunt schakelen. En 12A in totaal. Ik denk niet dat iemand zoveel stroom gaat gebruiken (144W op 12V!).

Een wat hogere spanning kan geen kwaad maar ik denk dat je daar het piekprobleem niet mee oplost, er komen dan nog clamp diodes bij. SOT-23 hoeft dan niet meer per se omdat er meer ruimte is op de losse modules. Volgens mij zijn er ook vrijwel geen FETs die 50V kunnen hebben en tegelijkertijd in SOT-23 zitten. Maar bij microcontroller aansturing is een logic level FET wel erg praktisch.

Op 30 september 2007 10:07:03 schreef MagicBox:

Nog even over de clamp diodes: Het zal werken, maar valt ook weer onder symptoom bestrijding. Tevens stook je vermogen weg in die diodes als de spikes erg hoog zijn. Je hoeft welliswaar geen zware diodes te nemen, maar het is toch een deel aan vermogen dat je weggooit. Zulk soort diodes moeten dien als bescherming voor foutsituaties, niet als oplossingen.

Bescherming tegen foutsituaties is sowieso een goed iets, maar is het ook niet zo dat de pieken juist niet meer ontstaan door de diode? Je hebt immers inductie in de draden die de stroom het liefst constant wil houden. Als de FET uitschakelt gaat de inductie spanning opbouwen om de stroom weer te kunnen laten lopen, wat niet gaat lukken zonder pad en een spike veroorzaakt.

Maar met een clamp diode is er nog steeds een pad voor de stroom en is het niet nodig de spanning hoog op te laten lopen, de spanning over de diode is genoeg. Kortom: voorkomt de diode de spanningspiek of sluit de diode de spanningspiek kort? Het ziet er beide hetzelfde uit, de piek is weg. Ik heb me dit wel vaker afgevraagd, inducties blijven toch wel lastig vaak. Misschien is het allebei wel hetzelfde maar zijn het verschillende manieren om het te zien.

Op 30 september 2007 12:16:40 schreef madwizard:

[...]Bij mij is er geen multiplexing, maar PWM op de FPGA betekent wel dat er nog steeds 12 (eigenlijk 16 met GND) draden naar de modules moeten. Want elke module moet onafhankelijk gestuurd worden. Zonder 'intelligente' module moet voor je elk kanaal los een draad maken.

Ik gebruik wel de beiden samen. Ik heb 48 uitgangen waar pwm opstaat maar de mux selecteerd 1 uit 8 voedingslijnen als matrix. Bij iedere omschakeling van de mux krijgen natuurlijk de 48 uitgangen ook een andere pwm waarde. mux en pwm zijn synchroon op elkaar afgesteld en daardoor bekom je 48x8 = 384 kanalen met elk zijn stuurlevel via pwm. Piekstroom wordt natuurlijk hoger dan bij niet multiplexen en daaom moet de pulsbreedte ook voldoen ( niet te lang zijn). Mijn berekeningen gaan daarbij uit van 128 usec max pulsbreedte en een duty-cycle van 1:8

Je bedoelt die FETs als sturing te gebruiken voor de andere FETs? Wel een beetje zonde van die FETs. Het zijn wel degelijk power FETs, ook al zijn ze klein. Het is niet een 2N7002 (BS170).

waarom niet? hierdoor heb je een vrij universeel printje die overal kan ingezet worden. Als het vooral een prijskwestie is kun je er eventueel een andere inplaatsen, mogelijks kan je bij het bestukken kiezen uit meerdere types. trouwens bij het routen kun je zelfs voorzien om die fet geheel weg te laten als er een andere driver offboard staat mits een soldeer brugje (2 bolletjes samen solderen).

Zoals ik zei zijn de huidige FETs gewoon power FETs. Niet in de orde van 50A maar dat is ook overkill. Ze kunnen 4,3A hebben als je ze goed open stuurt (4,5V) maar mijn doel is ongeveer 1A en dat gaat prima met 3,3V aanstuur logica. Afgezien van de pieken werkt een 1A stroom bijvoorbeeld prima, de FET wordt niet voelbaar warm. Veel hogere stromen zullen niet nodig zijn. Elk kanaal is 1 kleur, dus je hebt al 3A totaal per strip wat je kunt schakelen. En 12A in totaal. Ik denk niet dat iemand zoveel stroom gaat gebruiken (144W op 12V!).

Kijk daar zie ik juist het probleem. Al die stromen breng je samen op uw 2 layer printje. Als die draden wat lengte hebben zie ik daar blijvende problemen.

Op 30 september 2007 13:26:09 schreef fotoopa:

Ik gebruik wel de beiden samen. Ik heb 48 uitgangen waar pwm opstaat maar de mux selecteerd 1 uit 8 voedingslijnen als matrix. [...]

Dat zijn ook veel meer kanalen natuurlijk, in mijn geval is multiplexen onhandig, je weet ook helemaal niet wat voor LEDs eraan hangen. Bovendien zou het mooi zijn als er ook nog CCFL's op aangesloten konden worden door de inverter te PWMen.

waarom niet? hierdoor heb je een vrij universeel printje die overal kan ingezet worden. Als het vooral een prijskwestie is kun je er eventueel een andere inplaatsen, mogelijks kan je bij het bestukken kiezen uit meerdere types.

Maar de uitgangen zijn niet te gebruiken om direct LEDs aan te sluiten, want dan heb je weer het spanningspiek probleem. Dus dan zou het alleen zijn om de digitale PWM signalen uit de PWM wat meer te beveiligen tegen vreemde spanningen. De lange kabels blijven ook, je kunt nog steeds pieken krijgen dan, ook met digitale logica hoewel de stroom dan wel veel kleiner is.

Ik denk dat het dan makkelijker is een serieweerstand met een dubbele schottky naar de voeding te zetten als clamp, en gewoon 3.3V LVTTL als aansluiting te gebruiken. Waarschijnlijk worden het toch een paar seriele datalijnen en niet 12 stuks. De weerstand en schottky's beschermen dan ook tegen eventuele vreemde spanningen. Zoals free_electron hier gepost heeft.

Kijk daar zie ik juist het probleem. Al die stromen breng je samen op uw 2 layer printje. Als die draden wat lengte hebben zie ik daar blijvende problemen.

Oke wat dat stroom PWMen betreft zou dat kunnen kloppen, al weet ik niet of 4 lagen daar veel verbetering in zouden brengen. Je zou de schakelende signalen tussen grondvlakken kunnen zetten als afscherming maar het blijft een hoop stroom.

Ik dacht dat je het over FPGA's in het algemeen had op twee lagen, dat heb je wel eens eerder genoemd volgens mij.

free_electron

Silicon Member

Professioneel ElectronenTemmer - siliconvalleygarage.com - De voltooid verleden tijd van 'halfgeleider' is 'zand' ... US 8,032,693 / US 7,714,746 / US 7,355,303 / US 7,098,557 / US 6,762,632 / EP 1804159 - Real programmers write Hex into ROM

ik heb niet alle reacties gelezen en misschienheeft iemand dit al gezegd:

je hebt GEEN probleem n je systeem. je schakelt puur resistieve loads.

de spike die ziet komt door je labvoeding. een labvoeding heeft geen oneindig kleine interne weerstand ( dat wisten we al )

bovendien is dat niet alleen een ohmse weerstand maar een reactantie die daar staat.

elke voeding heeft een regellus. bij afname van piekstromen kan je dergelijke dingen aan het resoneren krijgen.

je moet ALTIJD in eendert welk circuit ook , of het nu batterij gevoed is of anders , een tank condensator vlak bij de load plaatsen om dergelijke 'zever' op te lossen.

ik zou beginnen om elke led slinger met een eigen draad nar een sterpunt te laten gaan. daar waar de draad aan de leds omt zet je een cap naar een common ground ( zo dicht mogelijk bij de source van je fets.

zo dus

+ ---+-------------------------+---|>|-|>|-|>|--SD-+- GND

| |___||______________|

| ||

|

|

|

+-------------------------+---|>|-|>|-|>|--SD-+- GND

|___||______________|

| ||

etc..

afhankelijk van welke stroom je trekt en wat je switching freq is zul je dat moeten aanpassen. begin met daar 0.47 uf keramisch te zetten , of 1 uF keramisch.

En een eindje draad heeft natuurlijk geen inductantie?

Volledig akkoord dat de voeding afgevlakt moet worden... maar clamps en/of slope control zullen nodig blijven.

@Free, ik vind het wel kort door de bocht om het af te geven op de voeding.

Er is geen enkele voeding met een oneindig lage uitgangsweerstand. Alle regelende feedback voedingen hebben dat vertoon, dat uitgangsspanningen kunnen gaan resoneren bij bepaalde belastingen. Granted, het wordt minder naarmate de regelfrequentie van een voeding hoger is. Maar een voeding met een regelfrequentie die 10 - 50 maal hoger ligt dan de afgeleide frequentie van een rise/fall-time van 5nS?

Met niet-geregelde voedingen A.K.A. accu's heb je te maken met een redelijke inwendige weerstand, maar die zal nooit van die belachelijk hoge terugslag spanningspieken gaan produceren.

Ik ben het met je eens dat degelijk ontkoppelen met tank elco's nodig is, ongeacht het soort voeding dat iemand zou gebruiken. De schakeling zou zowiezo tolerant moeten zijn ten opzichte van de gebruikte voeding, zodat de voeding dus NIET de oorzaak van dit probleem is/wordt.

Dit kan gedaan worden met de vele suggesties die al in dit topic zijn gedaan.

free_electron

Silicon Member

Professioneel ElectronenTemmer - siliconvalleygarage.com - De voltooid verleden tijd van 'halfgeleider' is 'zand' ... US 8,032,693 / US 7,714,746 / US 7,355,303 / US 7,098,557 / US 6,762,632 / EP 1804159 - Real programmers write Hex into ROM

Op 30 september 2007 17:20:41 schreef MagicBox:

Maar een voeding met een regelfrequentie die 10 - 50 maal hoger ligt dan de afgeleide frequentie van een rise/fall-time van 5nS?

inderdaad. dergelijke dingen bestaan niet ( tenware misschien met een BOP ... )

vandaar ook die condensatortjes.

die dingen doen 2 zaken :

1 - ze houden de hf spikes weg uit de voeding . met andere woorden ze zorgen dat de voeding de spikes niet ziet en er dus ook iet door verstoord kan worden. die caps staan er dus om de rotzooi weg te houden die NAAR de voeding zou gaan.

2- een voeding kan alleeen sourcen. niet sinken ( tenware dat het een 2 of 4 kwadrant voeding is of een BOP ). dus bij het afschakelen van een last krijg je rare effecten. een voeding heeft een inductantie. de stroom wil blijven lopen.. met als gevolg : tegen-emk. en dat kunnen wel steile spikes zijn.

dus daar opnieuw : capjes zetten en eventueel een zener diode over de voedingsrails zetten ( op je bord. niet aan de voeding. kwestie van de draadinductantie ook weg te halen.)

Ik heb net even wat getest met een aantal schottky's vrij dicht bij de FETs (bovenop de pinheader). Kathode aan de + van de labvoeding, anode aan de drains van de FET. Dan nog een 100uF elco + 100nF keramisch (had even niet groter liggen in through hole) ook vlak bij het printje tussen + en - van de labvoeding. De load (10 ohm) met de plus direct op de condensators, min via een <10cm draad op de drain van de FET.

Beetje zoals hier rechts dus, maar dan met schottky over de load in sper:

Hoewel ik eerder dacht dat de elco al het probleem aardig oploste bleek dat nu tegen te vallen, misschien dat bij eerder tests de FET alweer stuk was (is lastig te merken tijdens het testen, opeens kan ie stuk zijn).

De spike is wel wat minder maar nog steeds behoorlijk, de schottky's lijken niet veel uit te halen:

De zeners hadden een veel beter effect, daar was het probleem eigenlijk helemaal weg.

Spanning is hier niet zo hoog dus misschien komt de piek hier door de spanningsval over de schottky maar bij hogere spanningen blijft de piek ook flink stijgen, bijna proportioneel.

Misschien dat 100nF niet genoeg is in dit geval, voor zo'n snelle piek is misschien meer nodig. Aan de andere kant is de stroom maar 100mA, niet echt veel.

Ook is er nog geen gate weerstand, dat zou ook goed kunnen helpen maar dat is wat lastig te testen op dit printje.

Nog maar eens wat meer testen met hogere capaciteit, kon nu alleen even snel wat uitproberen.

De lus drain-diode-voeding-ontkoppeling-source moet absoluut zo klein mogelijk zijn. Je kan die evt. met opzet wat langer maken, en zien wat de invloed op de lengte van de spike is.

Je kan ook eens met andere diodes experimenteren, een good old 1N4148 bijvoorbeeld.

Naast de snubber zal je sowieso de slopes nog wat zachter moeten maken dmv. gate-weerstand. Hoeveel? Hangt van de duur van je spike af.

Let ook op of de meting wel betrouwbaar is, bij schakelend spul heb je met kortgesloten probe soms wel enkele volts p-p troep in de lucht.