Ik heb zelf ook een keer gekeken naar die mooie DDS chips van Analog Devices. De AD9834 maakt een sine, square en triangle output tot 37.5MHz (niet de oude datasheet pakken die maar 25MHz specificeerd), maar daar zit geen duty cycle adjustment op. Dat zou enkel met een hulp-DDS die de phase registers wisselt. Helaas heeft dat ook zijn beperkingen (delays, 2x DDS lijkt wat overkill, groot en duur voor zo'n feature)

Bovendien is ook de vraag of je een meer waveform outputs wil hebben, hoge frequenties of hoge resolutie. Die AD9834 heeft 'slechts' 28-bit frequentie tuning. Er zijn andere DDSjes die tot 32-bit gaan. Is toch een factor 16x nauwkeuriger, en dat vond ik nogal wat. (Het verschil tussen tientallen Hz of 1Hz tuning!)

Al die analoge chips zijn niet digitaal regelaarbaar, dus die vallen (voor mij doen) af.

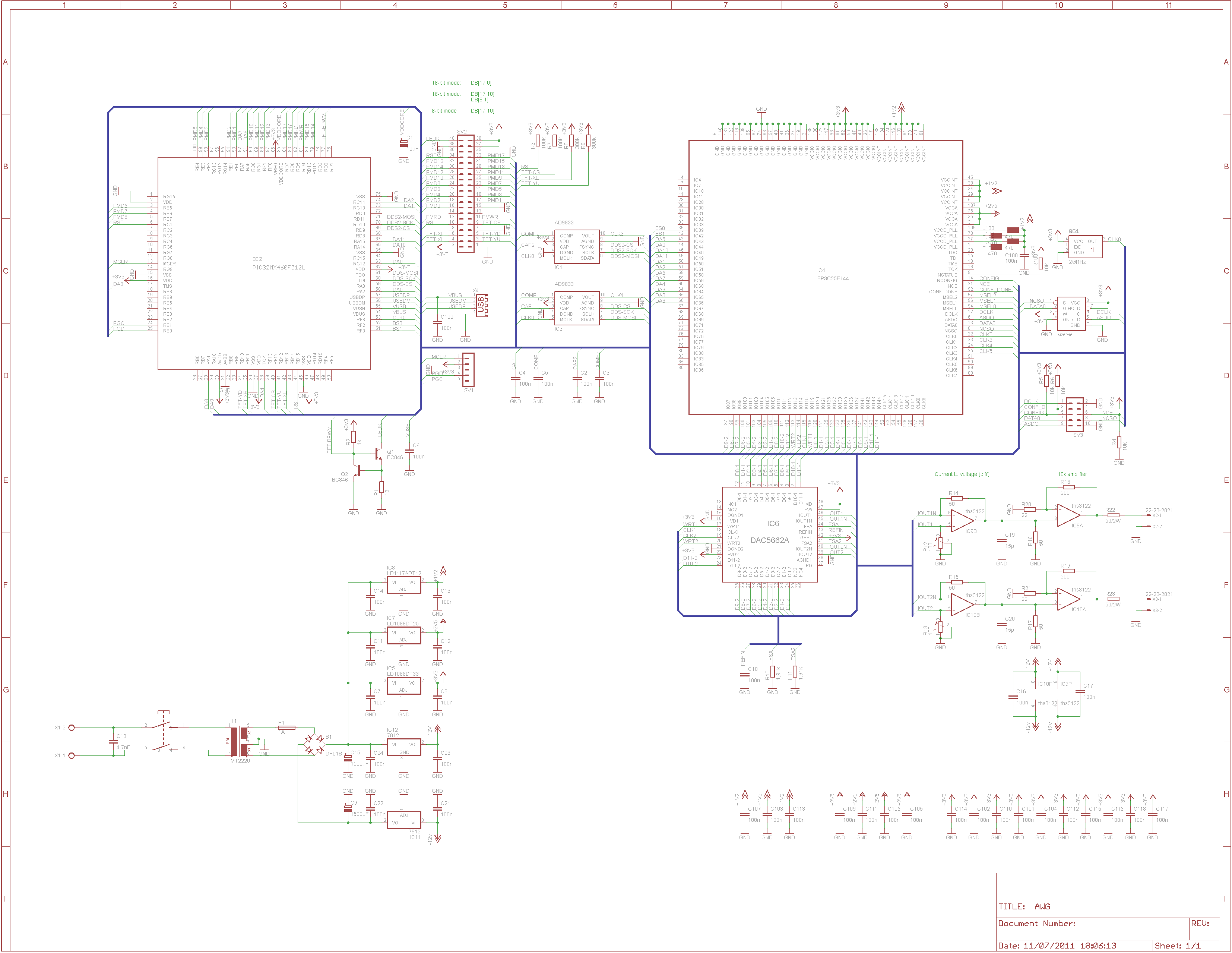

Ik denk dat je heel erg snel uitkomt bij een FPGA met een of ander grappig SRAM <> DAC constructie om je signal te genereren. Hier voor hoef je (in princiepe) geen 200MSPS DAC te halen.

De HP33120A werkt met een 12-bit DAC op 40MHz. Die functiegenerator heeft een max. output van 20MHz 15MHz (daar zit een 9de order Elliptical 17MHz of 7 order Bessel 10MHz filter achter - 20MHz sine is dus een 20MHz square wave uit de DAC). De FPGA stuurt aan welk adres uit het SRAM wordt uitgelezen. Die bepaalt daarmee de frequentie.

Door het SRAM heb je kan je al je eigen waveforms inladen, frequentie bepalen en heb je veel bits aan resolutie (die DDS chips zijn maar 10-bits, altijd nog minder dan 12). Frequentie-tuning lijkt me vrij lastig om te realiseren, wellicht daarom hun keuze voor de ASIC.

Wat je ook kan doen met zo'n opstelling is een modulation DAC toevoegen van 8-bit waarmee je de amplitude extern kan moduleren. Meeste high-speed DACs werken met output-current. Door de het referentieniveau van die weerstanden te verschuiven krijg je een andere gevoeligheid.. (en dus amplitude)

Voor zo'n aansturing heb je zeker een (vlotte) FPGA nodig om de benodigde signalen op te wekken, maar het is zeker een interessant project. Helaas heb ik niet veel FPGA's zelf aangeraakt, dus heb ik dat idee maar laten varen.

Ik zou echter eerst met zo'n DDS chip (mijn favoriet was de AD9834 omdat die met gemak 20MHz output kan doen, en triangle/square/wave heeft) testen hoe ver je komt. Zo'n HP33120A heeft natuurlijk ook features die je niet gebruikt of die nog veel software schrijven vereisen (en als je dat al niet wilt hoef je de hardware ook niet capable te maken).

Aanvulling:

Ik ben met knifter eens dat de eind-trap ook een klasse apart is. Wat voor specs aan amplitude wil je? Een 50 ohm + 50ohm verbinding betekent een 100ohm belasting. Met een amplitude van 15V output is dat 150mA op enkele MHz.

De service manual van de HP33120A is met weinig moeite op internet te vinden. Hetzelfde idee als uit dit topic: http://www.circuitsonline.net/forum/view/76624

Een Push/Pull trap (liefste klasse A omdat je zo min mogelijk vervorming wilt) die mogelijk DC-gecorrigeerd wordt door een opamp. Zo'n trap heeft waarschijnlijk ook weer koeling nodig, enzovoort.

Versterking zou je kunnen doen door verschillende vaste versterkingstrappen te doen (de HP heeft 5 trappen van elk 6dB hoger) + een VGA die je van 0 t/m 6dB precies kan regelen. Dan kan je elke amplitude maken die je maar wilt.

Ik zit hier te twijfelen of een analoge multiplexer of relais beter zijn om signalen te schakelen (ook b.v. output on/off switches). Solid-state chips zijn compact , maar hebben hoge weerstand en mogelijk niet het beste voor signalen. Je hebt speciale RF-relaisjes, maar die kosten nogal wat.