rew: Awesome bordje!

Ondertussen maak ik vorderingen met mijn 10G Ethernet project.

- Kloksignalen zijn als LVDS aanwezig en kunnen door de FPGA juist geroute worden.

- NEO430 controller geïmplementeerd in de FPGA

- Wishbone naar MDIO core gemaakt

- Wishbone naar I2C core gebruikt voor de SFP+ diagnose connectie

- Wishbone GPIO core gemaakt

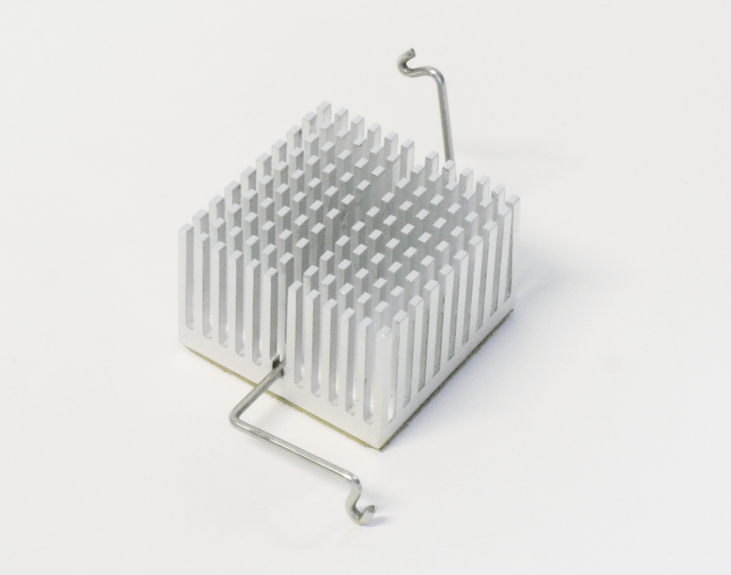

- Ik weet weer waarom ik de voedingen op de PCB heb overgedimensioneerd. Die print word WARM! Trekt nu 0.6A op 12V.

Zo langzamerhand kom ik op het punt waarop ik de gigabit interfaces ga testen. Eerst een near end loopback in de TLK10031, die de inkomende data vanaf de SFP+ module weer terug stuurt. Een far end loopback gaat door de "low speed" 3.125Gbps interface terug. Daarna heb ik een loopback mogelijkheid in de XAUI interface op de FPGA. Als dat allemaal werkt zijn alle gigabit lijnen operationeel. Dan kunnen we beginnen met de Ethernet packet interface. Fingers crossed!